Verilog HDL is a powerful hardware description language used for designing and simulating digital circuits.

It’s a must-know for anyone interested in hardware design, whether for building custom chips (ASICs), programming FPGAs, or working with embedded systems.

Learning Verilog empowers you to create complex digital circuits, from simple logic gates to advanced processors.

You’re likely here searching for the best Verilog course on Udemy, hoping to find a program that balances comprehensiveness with a practical approach.

Finding the perfect course among the many options available can be tricky, especially if you’re unsure where to start.

We’ve done the research for you, and we’re confident that Verilog HDL: VLSI Hardware Design Comprehensive Masterclass is the best overall Verilog course on Udemy.

This course offers a comprehensive introduction to Verilog, covering everything from fundamental concepts to advanced topics.

It goes beyond theory, providing real-world examples and hands-on projects that help solidify your learning.

While this course is our top recommendation, you may be looking for something more specific.

We’ve got you covered!

Keep reading to explore our comprehensive list of the best Verilog courses on Udemy, categorized for different learning styles and goals.

Verilog HDL: VLSI Hardware Design Comprehensive Masterclass

You’ll gain a firm understanding of fundamental VLSI concepts like design styles, ASIC design flow, and the importance of integration.

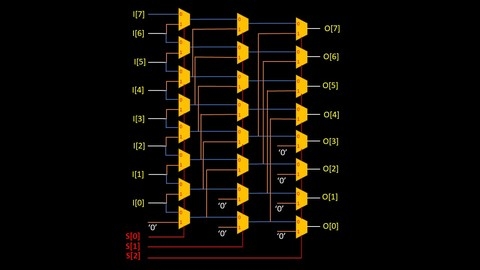

The course dives deep into Verilog HDL, covering a wide range of design styles, from dataflow to behavioral, and guiding you through the creation of complex circuits like full adders, multiplexers, and decoders.

You’ll also explore sequential logic, delving into the design of flip-flops, counters, and shift registers.

A significant portion of the course is dedicated to Finite State Machines (FSMs).

You’ll learn the differences between Mealy and Moore machines and gain hands-on experience designing them using Verilog.

Memory design is also explored, including the implementation of RAM structures.

While the course offers a broad scope, it would benefit from a more in-depth exploration of specific topics.

For example, a deeper dive into advanced ASIC design flow techniques, including verification methodologies and power optimization, would enhance its practical value.

Additionally, the course could benefit from more real-world examples and case studies to illustrate the application of the concepts learned.

It caters to beginners by offering a structured approach and comprehensive coverage of essential topics.

However, the addition of more advanced content and real-world applications would make it even more valuable for aspiring VLSI professionals.

Verilog for an FPGA Engineer with Xilinx Vivado Design Suite

This course provides a solid foundation in FPGA design, guiding you from the basics of Verilog to building complex projects using Xilinx Vivado.

You’ll start with the fundamentals of Verilog, covering data types, operators, and different modeling styles.

This comprehensive approach will give you a strong understanding of how to implement various design methodologies, including behavioral, structural, and gate-level modeling.

You’ll then move on to building essential digital circuits like adders, counters, and memory blocks.

The course emphasizes practical application, introducing you to using IP cores from Xilinx to streamline your design process and delving into the crucial world of Finite State Machines (FSMs).

You’ll also explore powerful debugging tools like the Integrated Logic Analyzer (ILA) and Virtual I/O (VIO) to effectively troubleshoot your designs.

The course doesn’t shy away from real-world applications, giving you hands-on experience by working on projects like implementing a UART interface, SPI communication, and PWM control.

Throughout the journey, you’ll learn about different FPGA architectures, including CPLDs and FPGAs, and concepts like LUTs (Look-Up Tables) and the Spartan 6 architecture.

While the course covers a wide range of topics, you might benefit from additional resources for deeper dives into specific areas like advanced Verilog concepts or particular FPGA architectures.

FPGA Embedded Design, Part 1 - Verilog

This course offers a solid introduction to the exciting world of FPGA design, focusing on the powerful Verilog hardware description language.

You’ll embark on a journey from the fundamentals of digital circuits, like logic gates and Boolean algebra, to more complex elements like multiplexers, demultiplexers, and adders.

The course emphasizes practical learning with hands-on projects that solidify your understanding of Verilog coding.

You’ll design a 4-bit adder and a counter, gaining valuable experience with the language’s syntax and structure.

The inclusion of multiple simulation tools like EPWave, GTKWave, and Modelsim ensures you’re equipped to test and refine your designs.

While the primary focus is on Verilog, the course briefly touches upon other hardware description languages like VHDL, broadening your perspective on the field.

This approach provides a balanced foundation, preparing you to explore more advanced FPGA concepts and projects.

This course is a great starting point for those interested in learning the basics of FPGA design.

The comprehensive curriculum, engaging projects, and exploration of different simulation tools will equip you with the essential skills and knowledge to confidently navigate the world of hardware design.

Verilog HDL Fundamentals for Digital Design and Verification

This Verilog HDL Fundamentals course offers a comprehensive introduction to the world of digital design and verification.

You’ll start by mastering the core concepts of Verilog, including data types, operators, and modules.

The course goes beyond the basics, guiding you through the different design styles – structural, dataflow, and behavioral – allowing you to choose the approach that best suits your needs.

Creating robust designs requires thorough verification, and this course equips you with the skills to build effective testbenches.

You’ll gain hands-on experience working with built-in primitives like multiplexers, demultiplexers, and tri-state buffers, fundamental components for building complex digital circuits.

The curriculum delves into both combinational and sequential logic, covering key circuits like adders, decoders, encoders, latches, flip-flops, and counters.

You’ll also explore the world of finite state machines (FSMs), learning to design and implement FSMs for various applications like sequence detectors and data transfer systems.

Throughout the course, you’ll gain practical experience using industry-standard tools like Intel Quartus Prime Lite and Modelsim.

Complete Verilog HDL programming with Examples and Projects

You’ll start with the fundamentals of Verilog HDL, learning the syntax, data types, and how to structure programs.

The course takes you through three levels of design description: gate-level, data-flow, and behavioral modeling, providing practical examples along the way.

You’ll build a 4x1 Mux and a full adder, learning how to utilize gate-level modeling to create basic logic circuits.

You’ll explore data-flow modeling with assign statements and operators, creating circuits like binary to Gray code converters.

The course dives deep into behavioral modeling, introducing you to procedural blocks and assignment statements to build clock generators, counters, and more complex circuits.

Then, you’ll delve into the world of sequential logic circuits, learning to design essential components like D-flip flops, T-flip flops, and JK flip flops.

You’ll build counters, pulse generators, and even explore the exciting realm of Finite State Machines (FSM).

You’ll learn to design FSMs using Mealy and Moore models, build a sequence detector, and create various clock dividers.

The course equips you with advanced topics like memory design and test bench creation, ensuring you can thoroughly test your circuits.

You’ll then apply your skills to engaging projects, including designing a memory controller, a FIFO (First-In, First-Out) buffer, and a Hamming code circuit for error detection and correction.

Finally, you’ll gain a solid understanding of FPGA (Field-Programmable Gate Array), its essentials, and how logic is configured.

This comprehensive course will equip you with the skills and knowledge needed to confidently tackle a wide range of hardware design challenges.

You’ll become a well-rounded Verilog programmer with a strong foundation in hardware design principles.

Mastering Digital VLSI, ASIC and Verilog Interview Questions

This syllabus outlines a comprehensive exploration of digital VLSI and ASIC design principles, focusing heavily on practical Verilog implementation.

You’ll dive deep into the fundamentals of asynchronous and synchronous resets, a critical aspect of robust system design.

The course also contrasts AHB and AXI bus protocols, providing you with the knowledge to choose the right architecture for your performance needs.

The syllabus is packed with practical design exercises.

You’ll learn to manipulate basic logic gates, design various types of counters (including a skip-by-3 counter), and tackle timing violations, a common challenge in digital design.

You’ll even explore the intriguing application of Fibonacci sequences in circuit design.

Beyond basic principles, the syllabus delves into advanced topics such as clock domain crossing implementations and the addition of soft resets to DFFs.

You’ll gain a strong understanding of the FIFO data structure, including how to calculate its depth for various scenarios.

The course also explores power optimization techniques, contrasting the power consumption characteristics of binary and Gray counters.

By implementing circuits such as a leading ‘1’ detector, a random delay circuit, and a circuit for counting ‘1’s in a bus, you’ll gain valuable hands-on experience.

This course will equip you with the necessary skills to confidently tackle complex digital design challenges and answer Verilog-related interview questions.

Building a Processor with Verilog HDL from Scratch

This course provides a comprehensive and hands-on approach to building a processor from scratch using Verilog HDL.

You’ll embark on a journey starting with the fundamentals of processor architecture, delving into essential components like the arithmetic unit and instruction register.

You’ll learn how to design and implement these components in Verilog, and you’ll gain practical experience with testbenches to verify your code.

The course progressively introduces key concepts, like addressing modes and memory management, leading you to build a fully functional processor by the end.

You’ll explore Verilog arrays and become familiar with using the Memory Generator IP for creating memory modules.

You’ll also learn to implement branching and jumping instructions, crucial for controlling the flow of your processor.

One of the standout aspects of this course is its focus on Register Transfer Level (RTL) design.

You’ll gain a deeper understanding of how RTL concepts translate into practical implementation through Verilog.

The course also covers Finite State Machines (FSMs) and their role in processor design, giving you a strong grasp of this essential concept.

It’s an excellent choice for those seeking a structured approach to processor design, with practical examples and exercises that solidify your understanding.

Verilog HDL Through Examples

You’ll gain a strong foundation in Verilog by starting with the fundamentals, like understanding how it differs from traditional programming languages and how it’s used to model everything from basic gates to complex microprocessors.

The course takes a hands-on approach, guiding you through building your first Verilog code with a simple OR gate example.

You’ll then delve into key concepts like registers and wires, learn to write a testbench to test your designs, and progress to creating sophisticated circuits like half-adders, full-adders, and carry-lookahead adders.

You’ll explore essential components like multiplexers and demultiplexers for signal routing and gain a deep understanding of flip-flop design, covering both SR and D flip-flops.

The course emphasizes practical skills, offering valuable resources like EDA Playground, a helpful online platform for Verilog coding and simulation, and EPWave, a tool for generating and analyzing waveforms.

This course is suitable for individuals seeking a thorough introduction to Verilog, regardless of their prior experience.

VSD - Pipelining RISC-V with Transaction-Level Verilog

This course takes you on a journey into the world of RISC-V processor design, using Transaction-Level Verilog (TL-Verilog) and the makerchip.com platform.

You’ll start with a solid foundation, learning the basics of RISC-V architecture and the crucial concept of pipelining.

Don’t worry if you’re new to TL-Verilog - the course will guide you through its nuances, making it accessible even to beginners.

Throughout the course, you’ll engage in hands-on exercises that solidify your understanding of TL-Verilog and its applications.

These exercises are designed to be engaging and challenging, helping you build a strong grasp of how to design and implement efficient pipelines using this specialized hardware description language.

You’ll also get to explore the makerchip.com platform, a valuable tool for simulating and testing your designs.

The course delves deep into the intricacies of pipeline design, exploring techniques like retiming and register bypass.

You’ll see practical examples, like the Fibonacci series, illustrating how pipelines work and how to optimize their performance.

The focus extends to understanding pipeline interactions, covering topics like time division multiplexing (TDM) which enables multiple data streams to share a single channel.

As you progress, you’ll gain a clear understanding of TL-Verilog’s hierarchy and interfaces, learning how to structure and connect different components in your design.

You’ll also have the opportunity to test your knowledge through a certification challenge, designed to put your skills to the test and demonstrate your mastery of the concepts covered.

You’ll have a strong foundation in pipeline design, a valuable asset for any hardware engineer working in the modern digital landscape.

Verilog HDL Interview Preparation Guide

This Verilog HDL Interview Preparation Guide is a comprehensive resource designed to equip you with the knowledge and skills needed to excel in technical interviews.

The course delves into a wide range of Verilog concepts, from fundamental operators and modeling styles to advanced FPGA architecture, providing a solid foundation for anyone seeking a career in digital design.

You’ll begin by exploring the intricacies of Verilog operators and modeling styles, learning how to describe FPGA design flows in detail and choose the appropriate design entry methods for your projects.

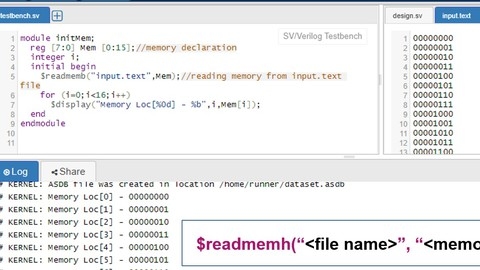

The course then dives into testbench fundamentals, teaching you how Verilog simulators schedule events and effectively utilize tools like $display, $monitor, and $strobe for verification.

Next, you’ll gain a deep understanding of essential data types like wire and reg, mastering their differences and applying them in your code.

You’ll explore the distinction between continuous and procedural assignments, blocking and non-blocking assignments, and intra and inter assignment delays, learning how to apply these concepts to achieve specific design goals.

The course also guides you through functions and tasks, demonstrating their implementation and effective utilization of output ports.

Moving on to flow control constructs, you’ll learn how to implement conditional statements using RTL and compare them with IF ELSE blocks.

You’ll analyze the effects of incomplete IF ELSE statements in both combinational and sequential circuits, ensuring you can create robust and predictable designs.

The course then delves into CASE statements, comparing them with IF ELSE and exploring the differences between CASE, CASEZ, and CASEX to choose the most suitable approach for your specific needs.

The course continues by covering common circuit fundamentals, teaching you about asynchronous and synchronous resets, the creation and avoidance of combinational loops, and the implementation of various types of counters.

You’ll then be introduced to the world of Finite State Machines (FSMs), exploring different types of FSMs and their implementations in Verilog.

You’ll learn to implement various sequence detectors, including overlapping and non-overlapping detectors, to create complex and sophisticated designs.

The course concludes with a comprehensive section on file I/O, teaching you how to read and write data from files in Verilog and utilize this functionality for design verification.

You’ll also gain a solid understanding of FPGA architecture fundamentals, exploring different PLD classifications and diving into the architectures of CPLDs and FPGAs, including the Spartan 6.

This Verilog HDL Interview Preparation Guide provides a comprehensive and practical learning experience, equipping you with the knowledge and skills to confidently approach technical interviews in the field of digital design.