VLSI design, the art of crafting intricate integrated circuits, is a cornerstone of modern technology.

These tiny chips power everything from smartphones and computers to cars and medical devices.

Learning VLSI opens doors to exciting careers in the semiconductor industry, allowing you to build the foundational components of our digital world.

Finding the right VLSI course on Udemy can be daunting.

With so many options available, you want a course that’s comprehensive, engaging, and taught by experienced professionals who can guide you through the complexities of this specialized field.

Based on our research, the Verilog HDL: VLSI Hardware Design Comprehensive Masterclass is the best overall course for VLSI on Udemy.

This course provides a solid foundation in Verilog HDL, a widely used hardware description language, and covers a broad range of VLSI design concepts, from basic logic gates to complex Finite State Machines (FSMs).

This is just the starting point for your VLSI journey.

Keep reading to discover more recommended courses tailored to your specific interests and learning goals, whether you’re a beginner eager to learn the basics or a seasoned professional looking to refine your skills in specific areas like static timing analysis, clock tree synthesis, or signal integrity.

VSD - Physical Design Flow

This course offers a comprehensive exploration of VLSI design, guiding you through the intricate process of physically creating a chip from start to finish.

You’ll begin with the fundamentals of floorplanning, learning how to strategically lay out the blueprint of your chip, optimizing cell arrangement and space utilization.

The course then delves into the critical aspects of placement, where you’ll learn how to position components strategically for optimal performance.

You’ll master the techniques of net-list binding, connecting components effectively, and optimizing placement through wire length and capacitance estimations.

Next, you’ll dive into the crucial area of timing analysis, ensuring your chip functions as intended.

You’ll explore both ideal and real-world clock scenarios, analyzing the timing behavior of your circuit under diverse conditions.

This includes understanding key concepts like setup timing, clock jitter, and data slew check, all essential for achieving accurate and reliable results.

The course then takes you into the fascinating world of clock tree synthesis, where you’ll build the network that distributes the clock signal across your chip.

You’ll master techniques like H-tree buffering, ensuring consistent clock signal delivery to all chip sections, and learn to address crosstalk, a common issue that can disrupt signal integrity.

Moving on to routing, you’ll learn to connect all components on your chip using wires, and the essential design rule check (DRC) to ensure proper wire layout without violating design rules.

You’ll also learn about parasitics extraction, analyzing the unwanted electrical effects of wires and components, and understanding the IEEE 1481 - 1999 SPEF format, a standard representation for these effects.

Throughout the course, you’ll develop a strong foundation in key concepts like static timing analysis (STA), signal integrity, and power planning, all critical for creating reliable and efficient VLSI designs.

You’ll also gain a solid understanding of concepts like utilization factor, aspect ratio, and decoupling capacitors, essential for designing robust and effective chips.

VSD - Static Timing Analysis - I

You’ll embark on a journey through the fundamentals of timing paths and arrival times, exploring how signals propagate through your circuits and how their speed impacts performance.

Delving into the world of setup and hold analysis, you’ll learn to ensure your circuits function reliably.

This involves mastering the concepts of required times, actual arrival times, and slack, utilizing timing graphs to pinpoint and resolve potential violations.

The course further guides you through the nuances of latch timing, crucial for circuits with sequential logic.

You’ll learn to analyze slew, load, and clock checks, ensuring signal integrity within your design.

Jitter analysis will equip you to understand the timing variability inherent in your circuits, a critical aspect for robust design.

You’ll also explore the impact of on-chip variation, a key factor in timing analysis.

Understanding how factors like etching and oxide thickness influence resistance, drain current, and delay, you’ll learn techniques like OCV (on-chip variation) timing and pessimism removal to account for these variations, ensuring accurate timing analysis.

You’ll have a solid grasp of the core concepts of static timing analysis, along with the skills to analyze setup and hold violations, latch timing, jitter, and on-chip variations, making you well-equipped to design robust and high-performance VLSI systems.

Verilog HDL: VLSI Hardware Design Comprehensive Masterclass

You’ll gain a firm understanding of fundamental VLSI concepts like design styles, ASIC design flow, and the importance of integration.

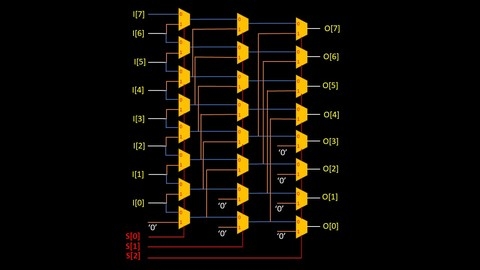

The course dives deep into Verilog HDL, covering a wide range of design styles, from dataflow to behavioral, and guiding you through the creation of complex circuits like full adders, multiplexers, and decoders.

You’ll also explore sequential logic, delving into the design of flip-flops, counters, and shift registers.

A significant portion of the course is dedicated to Finite State Machines (FSMs).

You’ll learn the differences between Mealy and Moore machines and gain hands-on experience designing them using Verilog.

Memory design is also explored, including the implementation of RAM structures.

While the course offers a broad scope, it would benefit from a more in-depth exploration of specific topics.

For example, a deeper dive into advanced ASIC design flow techniques, including verification methodologies and power optimization, would enhance its practical value.

Additionally, the course could benefit from more real-world examples and case studies to illustrate the application of the concepts learned.

It caters to beginners by offering a structured approach and comprehensive coverage of essential topics.

However, the addition of more advanced content and real-world applications would make it even more valuable for aspiring VLSI professionals.

VSD - Clock Tree Synthesis - Part 1

This course offers a comprehensive exploration of clock tree synthesis, a critical aspect of VLSI design.

You’ll gain a deep understanding of clock tree quality checks, focusing on essential parameters like skew, pulse width, and duty cycle.

The course goes beyond basic concepts, delving into power optimization techniques to help you minimize power consumption in your designs.

You’ll be introduced to the H-Tree structure, a widely used clock tree architecture, and learn the algorithm behind its effective skew minimization.

The course also guides you through the process of clock tree modeling and building, including the crucial aspect of clock tree buffering.

A key focus of the course is on the buffered H-Tree and the unique challenges it presents.

You’ll explore the PMOS/NMOS switching resistance difference in CMOS inverters and discover solutions for achieving resistance matching.

You’ll see how clock buffers affect pulse width and gain insights into different power components such as dynamic, short circuit, and leakage power.

Beyond technical skills, the course also prepares you for industry-relevant interviews by covering essential clock tree synthesis concepts.

You’ll gain a solid understanding of key topics like skew, buffer levels, latency, clock gating, and setup slack.

The course also dives into important areas like short circuit power, leakage current, and total chip power, equipping you with a holistic view of power consumption.

This course provides a valuable foundation in clock tree synthesis, equipping you with the knowledge and skills needed to excel in this specialized field.

VSD - Static Timing Analysis - II

You’ll master the intricacies of STA using industry-standard tools like sta-2 and OpenTimer.

This hands-on course focuses on building practical skills, not just theoretical knowledge.

The course kicks off by familiarizing you with the sta-2 and OpenTimer tools, guiding you through the creation of netlists and defining your project’s timing constraints.

You’ll learn to specify clock properties, input and output delays, and create comprehensive timing constraints.

Next, you’ll move into full register-to-register analysis, learning how to calculate required and actual signal arrival times.

The course delves into critical concepts like slack, pessimism, and engineering change orders (ECOs), empowering you to optimize your designs for optimal timing.

A significant portion of the course is dedicated to interface analysis, a crucial aspect of VLSI design.

You’ll explore various scenarios, including setup and hold time analysis, and learn to fix hold time violations with ECOs.

You’ll also gain proficiency in source synchronous interfaces, a common design technique in VLSI.

Moving on to clock gating, the course explores different types of gating and their impact on timing analysis.

You’ll learn to analyze active high and active low clock gating, as well as latch-based techniques and integrated clock gating cells.

The course then covers the critical topic of asynchronous reset design.

You’ll understand the role of reset synchronizers in resolving reset deassertion issues and gain experience with data-to-data setup and hold checks.

Finally, you’ll delve into latch timing, analyzing both positive and negative latch behavior.

The course touches on load and slew interdependence, providing a solid foundation in these important concepts.

Throughout the course, you’ll work through real-world examples and practical exercises.

You’ll create my_run.tcl scripts, my_netlist.v files, and my_netlist.timing files, gaining hands-on experience in setting up and analyzing complex VLSI designs.

VSD - Circuit Design & SPICE Simulations - Part 1

You’ll delve into the fundamental concepts of strong inversion and threshold voltage, exploring how the substrate potential influences these parameters.

You’ll gain a solid understanding of the different operating regions of NMOS transistors, including the resistive and saturation regions, and build a foundational knowledge of drift current theory.

But this course doesn’t stop at theory.

It then takes you straight into the practical world of SPICE simulations, guiding you through setting up your first simulations and understanding the language of SPICE.

You’ll explore technology parameters and standard technology files, and even learn how to simulate the effects of velocity saturation at different technology nodes.

This course will equip you to understand the behavior of transistors in different scenarios.

You’ll gain insight into how drain current varies with gate voltage for long and short channel devices, and delve into the important concept of velocity saturation drain current modeling, crucial for accurately predicting transistor behavior at high electric fields.

You’ll also explore the fundamental concept of CMOS voltage transfer characteristics and see how MOSFETs can act as switches, ultimately creating your own VTC (Voltage Transfer Characteristic) by merging the load curves of PMOS and NMOS transistors.

This course provides a strong foundation for anyone interested in circuit design and SPICE simulations, offering both theoretical knowledge and hands-on practical experience.

ASIC Bootcamp for VLSI Engineer: STA Basic Concepts

You’ll start with the fundamentals, understanding what STA is and how it predicts the timing behavior of your circuits.

Prepare to dive deep into delay calculation, where you’ll learn the essential techniques for ensuring your design meets performance requirements.

The course goes beyond theory, providing practical guidance on developing constraints, those crucial rules that govern the timing analysis process.

This knowledge is vital for optimizing your designs to meet tight performance targets.

You’ll then move on to timing verification, where you’ll learn to check if your designs meet the specified timing requirements.

The course explores different types of timing checks, including special checks for identifying potential problems that might otherwise go unnoticed.

You’ll also gain insight into the impact of crosstalk and noise, factors that can significantly affect timing performance, and learn how to mitigate their effects.

The course culminates in a thorough exploration of the STA methodology, providing a step-by-step approach to ensure your design is timing-correct before fabrication.

You’ll learn how to use a sign-off checklist, an essential tool for confirming your design’s adherence to all timing requirements.

This course will equip you with the knowledge and skills to confidently tackle the challenges of timing analysis in your VLSI design projects.

VSD - Signal Integrity

This course delves deep into the critical world of signal integrity, a crucial aspect of VLSI design.

You’ll be equipped to tackle the challenges of crosstalk, a phenomenon that can disrupt your circuits and hinder performance.

The syllabus provides a comprehensive overview of key concepts like noise margin and timing windows, essential for understanding the behavior of signals in complex integrated circuits.

You’ll explore the different ways crosstalk can impact your designs.

Imagine a scenario where one signal (the “aggressor”) disrupts another signal (the “victim”) on its path to the destination.

You’ll learn to predict these scenarios and employ techniques like shielding and adjusting drive strengths to minimize disruptions.

The course also addresses the often-overlooked issue of power supply noise.

You’ll learn how to design power mesh solutions and utilize decoupling capacitors to keep voltage drops in check, ensuring your circuits are protected from this subtle but impactful source of noise.

The syllabus emphasizes practical applications, including real-world examples of how crosstalk impacts setup and hold timing.

You’ll delve into techniques for calculating timing windows, identifying potentially unsafe glitches, and designing robust circuits resistant to noise.

You’ll also explore advanced topics like AC noise margin and the impact of crosstalk delta delay on clock skew, gaining a comprehensive understanding of the complexities of signal integrity.

By completing this course, you’ll have a solid foundation in signal integrity analysis and design.

You’ll be equipped to identify and solve real-world problems related to crosstalk, power supply noise, and timing issues.

This knowledge will be invaluable in your VLSI design career, empowering you to create high-performance and reliable circuits.

VSD - Clock Tree Synthesis - Part 2

You’ll start with a solid foundation, learning the essential optimization checklist for clock trees, covering techniques for reducing leakage and short-circuit currents.

This foundation lays the groundwork for understanding the impact of uneven clock endpoint distribution, a challenge you’ll learn to tackle by designing efficient clock trees even for millions of endpoints.

The course then delves into the crucial aspect of power-aware clock tree synthesis.

You’ll be introduced to clock gating cells and delay tables, mastering their usage and exploring various clock gating techniques.

These techniques, using AND, OR, and universal NAND gates, are then analyzed in the context of real chip designs, giving you a clear understanding of their impact on power consumption.

The final section focuses on static timing analysis, covering both setup and hold timing analysis.

You’ll gain a strong grasp of data arrival and required times, slack, and the impact of unbalanced skew on timing constraints.

This course is well-structured and provides a strong foundation in clock tree synthesis.

The practical examples and clear explanations make it a valuable resource for anyone seeking to master this essential aspect of VLSI design.

Digital Timing Basics for VLSI Interview & SoC Design

This course is a deep dive into the critical world of digital timing in VLSI design.

You’ll learn the foundational concepts that are essential for building complex System on Chip (SoC) designs and for confidently tackling technical interviews.

Starting with the basics of flop timings – like set-up time, hold time, and clock-to-Q delay – you’ll progressively delve into how these concepts apply throughout the design process, from logic implementation to physical layout.

One of the strengths of this course is its focus on real-world scenarios.

You’ll explore how to analyze and fix timing violations that can occur due to factors like clock skew and data path delays.

You’ll learn techniques to optimize designs for better latency and gain a deeper understanding of how frequency and voltage impact timing in real-world SoCs.

The course also covers the complexities of timing concepts in advanced structures, like latches and clock gating circuits.

But this course goes beyond theory.

You’ll find its real power in its focus on interview preparation.

You’ll be equipped with the knowledge and tools to confidently answer common interview questions related to timing concepts.

You’ll learn to calculate timing margins, analyze set-up and hold time conditions in various scenarios, and understand the impact of different design choices on timing performance.

You’ll even learn to dispel common misconceptions about timing concepts.

This course offers a comprehensive and practical approach to mastering digital timing in VLSI design.

Whether you’re aiming for a successful career in this field or seeking to strengthen your interview skills, this course provides the essential knowledge and insights you need to succeed.